一、基本概念和特点SPI Flash芯片是一种基于SPI(Serial Peripheral Interface,串行外设接口)协议的非易失性存储器,用于存储固件、配置信息、日志文件等需要持久保存的数据。其基本特点包括: - 非易失性存储:断电后数据不丢失,这使得它非常适合用于存储固件、配置文件、日志数据等。

- 高速读写:支持快速的数据读写操作,SPI Flash支持高速数据读写操作,提高了系统的整体性能。

- 低功耗:适用于电池供电的设备。

- 小体积:便于集成到各种电子设备中,SPI Flash芯片具有较小的体积和较低的成本,适合大规模生产和应用。

- 多种容量选择:从几十KB到几百GB不等,满足不同应用需求。

- 耐用性强:许多SPI Flash产品支持数十万次的擦写周期,这对于嵌入式系统来说是一个重要的特性。

- 多种容量选择:SPI Flash的容量可以从几十KB到几百GB不等,常见的容量有1MB、2MB、4MB、8MB、16MB、32MB、64MB、128MB、256MB、512MB、1GB、2GB、4GB、8GB、16GB、32GB、64GB等。

- 接口速度灵活:SPI Flash支持不同的接口速度,从标准的SPI速度(如1MHz、2MHz、4MHz、8MHz、10MHz等)到高速SPI(如20MHz、30MHz、40MHz、50MHz等),甚至更快。

- 多种封装形式:SPI Flash芯片有多种封装形式,包括TSSOP、SOIC、QFN、WLCSP等,以适应不同的电路板布局和空间要求。

- 低电源电压要求:SPI Flash通常只需要很低的电源电压,如3.3V或1.8V,这使得它非常适合电池供电的便携式设备。

二、工作原理

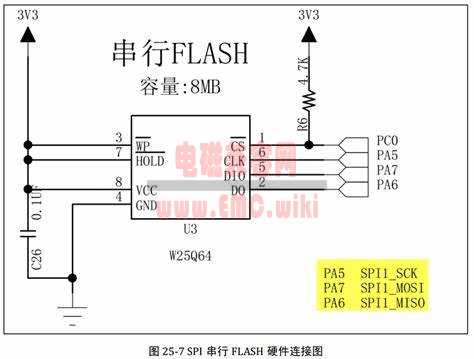

SPI Flash使用SPI总线进行数据传输,这是一种高速的、全双工的、同步的通信协议。它只需要四根线: - SCLK(时钟线):用于传输时钟信号,控制数据的同步传输。

- MOSI(主设备数据输出,从设备数据输入):用于主设备向从设备传输数据。

- MISO(主设备数据输入,从设备数据输出):用于从设备向主设备传输数据。

- SS(从设备选择):用于选择通信的从设备,实现一主多从的通信方式。

SPI Flash芯片通过SPI总线与主机设备进行通信。其工作原理主要包括以下几个方面: - 内部结构:SPI Flash芯片内部包含多个存储单元,这些存储单元按特定方式组织,通常以字节或页为单位进行读写操作。

- 逻辑操作:主机设备通过SPI总线向SPI Flash发送读取、写入和擦除等指令。SPI Flash根据接收到的指令执行相应的操作,并将结果通过SPI总线返回给主机设备。

- 数据传输:SPI Flash使用四根信号线(时钟线、数据输入线、数据输出线和片选线)进行数据传输。时钟线用于同步数据传输,数据输入线用于主机设备向SPI Flash发送数据,数据输出线用于SPI Flash向主机设备返回数据,片选线用于选择通信的从设备。

三、常见问题及解决方案- 辐射发射问题:SPI Flash芯片在工作时可能会产生辐射发射问题,影响设备的电磁兼容性。解决方案包括优化滤波电容布局、修改滤波参数、使用屏蔽罩等。

- 读写错误:在使用SPI Flash芯片进行读写操作时,可能会遇到读写错误的问题。这通常是由于时序不匹配、电压不稳定等原因造成的。解决方案包括调整时序参数、稳定电源电压等。

综上所述,SPI Flash芯片以其独特的优势和广泛的应用场景在嵌入式系统和便携式设备中发挥着重要作用。在使用过程中,需要注意其使用注意事项和常见问题,并采取相应的解决方案以确保系统的稳定性和可靠性。 |