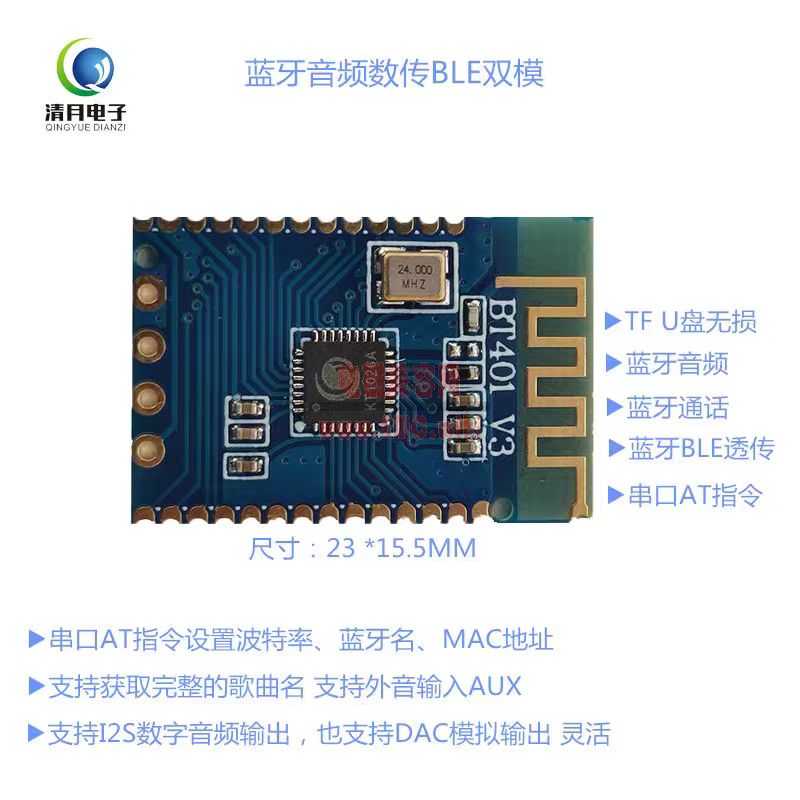

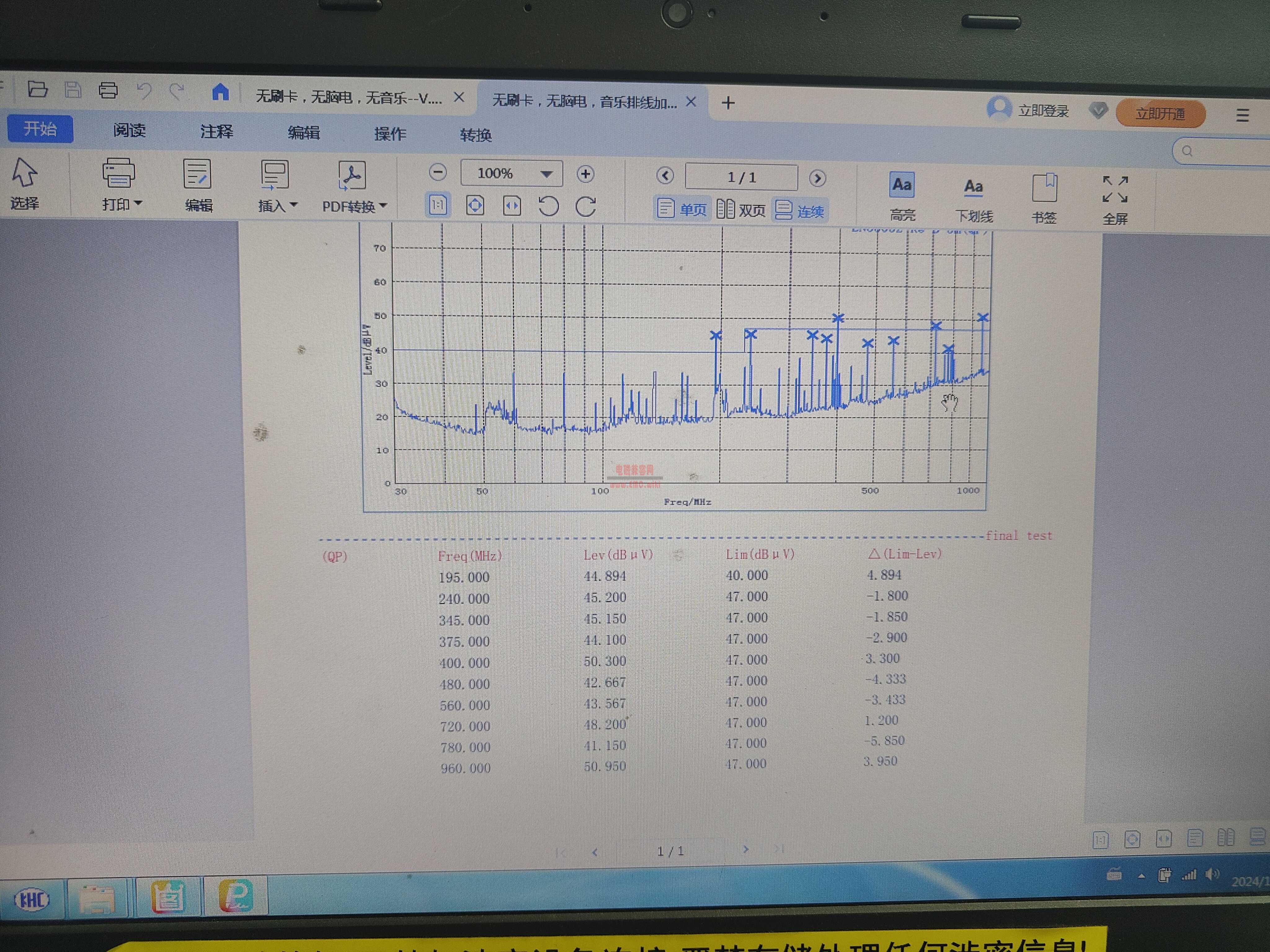

问:如上图所示蓝牙模块KT1026A,200-1000M之间会不会是蓝牙模块晶振的倍频?例如,240MHz、720MHz、960MHz 辐射干扰

答:蓝牙模块KT1026A是一个功能丰富的蓝牙音频模块,虽然无法直接找到其模块框架的详细官方描述,但根据同类产品和蓝牙模块的一般结构,可以推测其框架至少应该包括USB PHY,那么,这个蓝牙模块KT1026A完全有可能包括240MHz、720MHz、960MHz 辐射干扰。

USB PHY的时钟频率

USB PHY(物理层)的时钟频率可以根据不同的USB标准和应用场景而有所不同。以下是根据公开发布的信息整理的USB PHY时钟频率的一般情况:

一、USB 2.0- 在USB 2.0标准中,PHY层的时钟频率通常与数据传输速率密切相关。

- USB 2.0的高速模式(High-Speed Mode)数据传输速率为480Mbps,但具体的时钟频率可能因实现和芯片设计而异。

二、USB 3.0 及更高版本- 对于USB 3.0及更高版本(如USB 3.1、USB 3.2),PHY层的时钟频率更加复杂,因为这些标准支持更高的数据传输速率,并且可能采用多种时钟频率和调制方式。

- 以USB 3.0为例,其PIPE PHY(SerDes = PCIe Gen2)的数据线宽度和接口频率是可配置的。根据配置的不同,时钟频率也会有所变化。例如,在某些配置下,时钟频率可能达到数百MHz甚至更高。

- 对于具体的时钟频率值,如480MHz、500MHz等,这些可能是特定实现或芯片设计中的时钟频率。然而,这些值并不是USB PHY的固定时钟频率,而是可能因不同的芯片、设计或应用场景而有所变化。

三、其他考虑因素- 时钟源:USB PHY的时钟可能来源于内部振荡器(如RTC时钟)或外部时钟源。这些时钟源的频率和稳定性会影响PHY层的性能。

- 时钟管理:在现代USB芯片中,通常包含时钟管理单元(如PLL)来生成所需的时钟频率。这些时钟管理单元可以根据需要调整时钟频率,以满足不同的数据传输速率和功耗要求。

- 协议开销:在USB通信中,协议开销(如数据包头、校验和等)会占用一部分带宽。因此,实际的数据传输速率可能低于理论上的最大传输速率,这也可能影响PHY层的时钟频率选择。

四、总结由于USB PHY的时钟频率可能因多种因素(如USB标准、芯片设计、应用场景等)而有所不同,因此无法给出具体的时钟频率值。在实际应用中,建议参考具体芯片的规格书或技术文档来获取最准确的时钟频率信息。同时,也可以咨询芯片供应商或曾工 139 2899 3907获取更详细的指导。 |